## 國立彰化師範大學 97 學年度碩士班招生考試試題

系所:電子工程學系碩士班 組別:乙組 科目:邏輯設計

☆☆請在答案紙上作答☆☆

共2頁,第1頁

- 1. The inputs of *A*, *B* and *C*, *D* represent the binary numbers in the range 0:3. Show a truth table such that *w*, *x*, *y*, and *z* represent a binary number in the range 0:15 that equals to the magnitude of the multiplication product of the two inputs.

- 2. Show the decimal equivalent of the binary number 10010101 that is interpreted as

- (a) Unsigned binary

5%

(b) Signed binary (2's complement)

5%

3. Prove whether the following Boolean functions of f and h are equal or not.

10%

$$f(x, y, z) = xz' + x'z + yz$$

and  $h(x, y, z) = (x + z)(x' + y + z')$

4. Simplify each of following expressions using only the axioms of Boolean algebra:

(a)

$$f(a, b, c, d) = ab + bcd + ab'c' + abd + bc + a'bc$$

5%

(b)

$$g(A, B, C, D) = (A + B)(B' + C)(A + C + D)(A + B + D')(A + C + D')$$

5%

- 5. Referring to the function f(w, x, y, z) = (w' + x)(y + z)(w' + y)(x + y' + z)

- (a) Derive the SOP (Sum of Product) and POS (Product of Sum) canonical forms.

5%

(b) Using NOR gates to implement the function *f*.

5%

6. Using the Karnaugh map method to find the minimum Sum-of-Product expressions for

(a)

$$F(a,b,c,d) = \sum_{m} (3,4,9,13,14,15) + \sum_{d} (2,5,10,12)$$

5%

(b)

$$g(w, x, y, z) = w'yz + xy'z + wy + wxy'z' + wz + xyz'$$

5%

- 7. Using the 8-to-1 and 4-to-1 multiplexers to implement the following functions.

- (a) f(a, b, c, d) = b'c'd' + bd + a'cd

5%

(b)

$$F(x, y, z) = \prod_{M} (0, 2, 4)$$

5%

## 國立彰化師範大學 97 學年度碩士班招生考試試題

系所:電子工程學系碩士班 組別:乙組 科目:邏輯設計

☆☆請在答案紙上作答☆☆

共2頁,第2頁

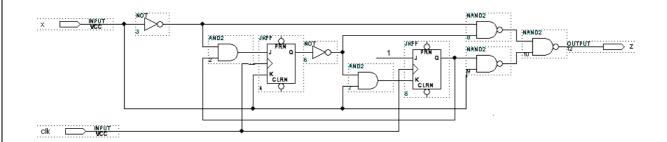

8. Derive the *next state equation*, *output function*, and *state diagram* of the following sequential circuit.

B.

9. Reduce the following system to one with the minimum number of states?

10%

| A. | C.S. | N.S. |     |   |  |  |  |  |  |

|----|------|------|-----|---|--|--|--|--|--|

|    |      | X=0  | x=1 | z |  |  |  |  |  |

|    | Α    | С    | Α   | 1 |  |  |  |  |  |

|    | В    | F    | Α   | 1 |  |  |  |  |  |

|    | С    | Α    | Е   | 0 |  |  |  |  |  |

|    | D    | С    | В   | 1 |  |  |  |  |  |

|    | Е    | D    | D   | 1 |  |  |  |  |  |

|    | F    | В    | Е   | 0 |  |  |  |  |  |

| C.S. | N.S.    |   | Z       |   |

|------|---------|---|---------|---|

|      | X=0 x=1 |   | X=0 x=1 |   |

| Α    | Α       | Е | 0       | 0 |

| В    | F       | D | 0       | 1 |

| C    | Α       | С | 0       | 0 |

| D    | F       | D | 0       | 1 |

| Е    | O       | Е | 0       | 0 |

| F    | Α       | С | 0       | 0 |

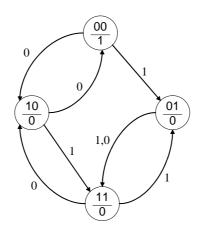

10. Referring to the following state diagram to design the sequential logic circuit using T-type flip-flops.